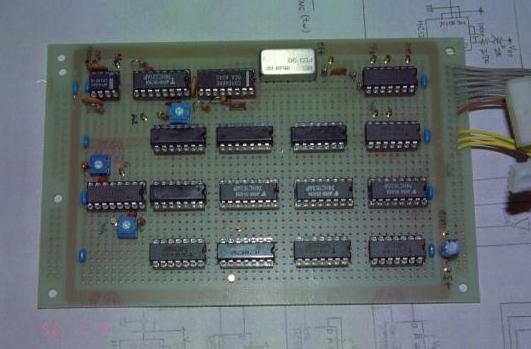

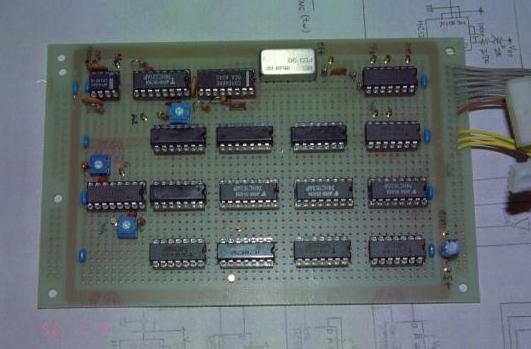

2.タイミング発生部の試作

タイミング発生部だけでICが15個くらいになり多少規模が大きくなるので、一度

タイミング発生部のみ単独で作成し、動作をさせて様子を見てみることにした。

回路を流れる信号の周波数で高い部分は28MHz位なので74HCのロジックICでで十分

賄えるものと思われる。

ユニバーサル基盤の上に組み上げてみたのがこれだ。

LM1881で水平同期信号を分離した後、HC211で垂直帰線時間中に含まれる等価パルス

を除去した水平同期信号(15kHz)をPLLで捕まえて、その周波数に同期した、910倍

(14.3MHz)のA/D変換用のクロックとラインメモリの書き込みパルス、1820倍(28.6MHz)の

D/A変換用クロックと、ラインメモリの読み出しクロックを作っている。

A/D変換用のクロック(14.3MHz)をHC163で455分周して、HC123でパルス幅を調整し

水平同期信号(31kHz)として出力される。また、ラインメモリの読み出しリセット

信号(31kHz)となり、これを、2分周してラインメモリの書き込みリセット信号(15kHz)と

PLLへのフィードバックとなる。

なお、ラインメモリのリセットクロックはD/A変換用のクロックでタイミングを

揃えられている。

LM1881で分離した垂直同期信号は、HC123でパルス幅を調整しそのまま垂直同期信号

として出力される。

資料として使った、トラ技SPECIAL No5の回路ではPLLは位相比較でMC4044、VCOに

74F04のインバーターゲートを2つ使った回路で構成してあるが、この回路はうまく

作り込めるかどうかわからないので(指定のバリキャップが入手できないというう問題も

あった)。位相比較用でMC4046(内部にVCOも持っているが28MHzは賄えない)、VCOに

MCL社のPOS-50(秋月で購入)を使用した。高周波用のVCOをこのような用途に使用す

るのはもったいないという気もするが・・・。

HC163とラインメモリのリセットタイミング発生部周りはほぼ資料の回路通りである。

回路図は

こちら

(GIF形式:約45kByte/1999.10.24一部修正)

戻る

(C)1995,96,99 MIGITA ELECTRIC WORKS